고정 헤더 영역

상세 컨텐츠

본문

FET에서 이해하기 어려운 개념중의 하나가 핀치오프라는 현상이다. 현상적으로 이해 못할 것은 눈곱 만치도 없다. 왜냐하면 자료마다 설명이 넘쳐나기 때문이다. 그러나 실족하는 부분은 바로 핀치오프 현상을 일으키는 핀치오프 전압이 어떤 때는 드레인 전류를 일정하게 유지시켜 주는 분기점 전압이 될 때도 있고, 어떤 때는 드레인 전류가 전혀 흐르지 못하는 분기점 전압도 된다는 점 때문에 난해 해 진다. 어찌보면 서로 모순되어 보이는 현상을 일으키는 전압이 똑 같이 핀치 오프전압이 될 수 있는가!!

서로 이질적인 현상을 일으키는 전압을 동일하게 핀치 오프전압 이라고 했는지 궁금해한 사람도 있을 것이지만 현실적으로 속 시원하게 설명해 준 곳은 찾기 어렵다. 문제 의식조차 없었던 것도 사실이다.모순해결의 관점에 맞추어 설명을 읽어 보면 작은 도움이 될 것 같다.

MOSFET에 비해서는 활용도가 떨어지나 JFET의 동작 특성과 용도를 알면 여러 종류의 FET를 대충 파악 할 수는 있게 된다. 많이 널리 선호되는 소자는 MOSFET 이다. 그러나 기본기의 시작은 JFET 부터다. P 와 N 채널이 있는데 N채널을 중심으로 설명을 한다.

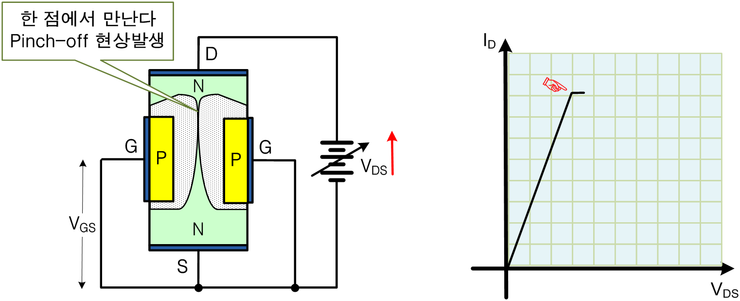

아래 그림의 JFET에서 보는 바와 같이 P 와 N의 접합 부근에서는 다이오드의 PN접합과 같이 공핍층 형성이 자연스럽게 된다. 이런 공핍층을 확산에 의해 생겼기 때문에 확산 공핍층이라고 구별해 불러주는 곳도 있다. JFET 특성을 파악하기 위해서 전압을 인가해 주는데, 바이어스 ( Bias : 직류전압을 건다 )를 거는 것은 드레인-소스 간( VDS ) 게이트-소스간의 전압( VGS )을 걸어 주게 된다.

두 전압을 서로 변화 시키면 변수가 두 개가 되어 뇌가 따라가기 복잡하기 때문에 두 군데 전압을 변화시키는 것 보다 한 군데는 고정으로 전압을 인가하고, 한 군데 전압을 변화시켜 어떤 특성이 보이는지 고려해 줘야 사고하는데 쉽다.

먼저 게이트-소스간 전압을 0V로 고정시키고, 드레인-소스 간 전압( VDS )을 증가하는 방향으로 변화 시키면서 어떤 특성을 뽑아 낼 수 있는지 지켜본다. 출력쪽 전압을 증가시켜가면서 출력의 전류를 추적해 내는 것을 출력특성 이라고 해 준다.

① 게이트-소스간 전압( VGS )을 0V로 고정시키고, 드레인-소스 간 전압( VDS )을 인가하지 않는다.

드레인과 소스간의 전류 ( ID ) 가 흐르지 않는다.

② 게이트-소스간 전압( VGS )을 0V로 그대로 고정시키고, 드레인-소스 간 전압( VDS )을 증가시키면서 인가 한다.

드레인과 소스간의 전류 ( ID ) 가 흐르기 시작하는데 드레인-소스 간 전압( VDS )이 증가하는 것에 비례 해서 증가한다. 증가선을 이상화 시켜 선형적으로 증가하는 것으로 간주해 준다. 그런데 여기서 JFET의 구조가 어떻게 변하는가를 주목해야만 한다. 드레인-소스 간 전압( VDS )이 증가하는 것에 맞추어 드레인과 게이트 간에는 역방향 전압이 점점 강해지므로 마치 다이오드의 PN 접합처럼 역방향 바이어스가 증가되면 공핍층이 증가된다.

게이트와 소스간에 존재하던 공핍층이 크게 점점 자라나기 시작한다. 이 때는 확산에 의한 공핍층으로 부터 더 증가하게 되는데, 이는 직류전압 ( 바이어스 )를 걸어 주었기 때문에 일어난 현상이었다. 그래서 이때의 공핍층을 바이어스 공핍층이라 세분해 준다.

③ 게이트-소스간 전압( VGS )을 0V로 계속 고정시키고, 드레인-소스 간 전압( VDS )을 이전 상태 보다 증가시키면서 인가 한다.

드레인과 소스간의 전류 ( ID )의 추세가 계속 증가하는 방향으로 커진다. 게이트와 소스간에도 공핍층이 더 크게 확대된다.

④ 게이트-소스간 전압( VGS )을 0V로 끝까지 고정시키고, 드레인-소스 간 전압( VDS )을 더욱 높여 인가해 가기로 한다.

드레인-소스 간 전압( VDS )을 어느 순간까지 높여가다 보면 드레인과 소스간의 전류 ( ID )는 더이상 증가하기를 포기하고 거의 평탄해 지는 구간이 생기게 된다. 또한 이때 JFET의 상태를 보면 게이트 부분에서부터 자라 나가던 공핍층 양쪽이 한 점에서 서로 맞닿는 현상이 발생하게 된다. 이 때를 가리켜서 핀치오프 ( Pinch-off ) 상태가 되었다고 지칭해 준다.

핀치오프 이후에 편의상 특성 곡선이 평탄하다고 했는데 실제로는 약간의 기울기를 가지고 상승하는 추세를 그린다.

핀치 오프 ( Pinch-off )라는 말은 아래 그림과 같이 엄지와 검지를 맞잡았을 때, 마치 한 점에서 두 손가락이 마주치는 것처럼 되는 형태를 의미한다.

그런데 이 지점에서 이해하기 어려운 점이 딱 버티어 우리를 곤란하게 만든다. 위의 실험에서 그래프를 보면 드레인과 소스간의 전류 ( ID )는 증가하지 않지만 계속 일정하게 흐르는 것을 볼 수 있는데, 우리의 편견으로는 어떻게 공핍층이 생기는데 전류가 흐를 수 있냐는 것이다. 전류가 흐르지 않는 상태로 다이오드의 역방향 바이어스에 순치된 우리의 이성은 '공핍층= 절연체 일 것'이라는 편견에 찌들어 여기서부터 헤메이게 되었던 것이다. 핀치오프 ( Pinch-off ) 이후로는 채널이 막혀 전류가 전혀 흐를것 같지 않은데 어떻게 전류가 흐른단 말인가?

어떤 사람들에겐 이게 고민이고 풀리지 않는 숙제 같은 부분이다.

다이오드의 역방향 바이어스로 인한 공핍층과는 다른 변수가 있다 그것이 무엇일까? JFET의 동작에서 핀치오프 ( Pinch-off ) 현상이 일어날 때의 구조를 다시 한번 검토해 보자.

증가하는 드레인-소스 전압에 의해 핀치오프가 걸린 때는 드레인과 게이트 사이에는 공핍층이 서로 맞닿아 , 드레인과 소스사이에 전류가 흘렀던 채널이 공핍층으로 막힌 것이 분명하지만, 드레인과 소스 사이에는 강한 전압이 걸려 전계가 작용하고 있다는 사실을 염두에 두어야 한다.

강한 전계가 작동하고 있다는 것은 전자가 공핍층을 재빠르게 건너가 버릴 수 있는 유인책이 아주아주 충분하다는 의미를 갖는다. 마치 이루어 질 수 없는 남녀간의 사랑이 음력 칠월 칠석 까마귀, 까치가 만들어 준 오작교( 烏鵲橋 )로 견우와 직녀가 만나는 것처럼 전압 ( 전계 )은 마치 오작교의 역할을 수행 한다고 생각하면 된다. 강한 사랑은 국경을 초월 하듯이 반도체에도 이와 비슷한 현상이 있는 셈이다.

그렇다면 이런 느닷없이 보이는 주장은 근거가 있는가? 그렇다 우리는 이미 BJT 동작특성을 공부할 때, 어떤 조건이 성립만 하면 공핍층도 뚫어 버리고 지나가는 전자에 대해 전제하고 있었다. BJT를 활성영역에서 동작시키기 위해 아래와 같이 직류전압을 걸었다는 것을 상기 하기 바란다.

일단 베이스-컬렉터 사이에 공핍층이 보이는가?

베이스와 에미터 사이는 순방향 바이어스이기 때문에 에미터에 있는 전자가 뭉텅이 채 베이스로 건너간다. 반도체 제작 공정상 베이스는 얇게 만들고 불순물 농도를 에미터 보다 낮게 가져 간다. 베이스영역에 있는 낮은 농도의 정공과 재결합한 전자를 제외하고 에미터로 부터 대거 이주한 전자는 짝이 없는 홀아비 처럼 갈데라고는 베이스-컬렉터 단의 공핍층 쪽 밖에 없게 된다.

이런 공핍층을 건너는데에는 강력한 유인이있어야 비로소 가능해 진다. 루비콘 강을 앞에 두고 카이사르가 황제의 야망을 불태우면서 건너 갔듯이 전자는 컬렉터 쪽에 +전압에 의한 강력한 전계로 인해 질풍노도( 疾風怒濤 )와 같이 공핍층을 건너 갈 것이다. 해답은 강력한 전압에 의한 전계가 있어야 전자가 공핍층을 뚫고 지나갈 수가 있다. BJT와 마찬가지로 JFET도 핀치오프 이후로 이런 현상이 발생하는 것이다. 그래서 반도체소자는 비슷한 면이 있는 것 같아 보인다. 그렇다고 공핍층을 도체라고 간주하면 오해 중의 오해이다.

이런 사정이라면 MOSFET의 Depletion 형과 Enhancement 형도 비슷한 동작을 할 것으로 기대 해도 된다. 기본적 동작 하나를 알면 나머지는 거져 먹기식이 된다. 전위차가 존재한다면 전자는 공핍층을 빠르게 가로질러 간다는 명제하나 기억하기로 한다.

FET에서 이해하기 어려운 개념중의 하나가 핀치오프라는 현상이다. 현상적으로 이해 못할 것은 눈곱 만치도 없다. 왜냐하면 자료마다 설명이 넘쳐나기 때문이다. 그러나 실족하는 부분은 바로 핀치오프 현상을 일으키는 핀치오프 전압이 어떤 때는 드레인 전류를 일정하게 유지시켜 주는 분기점 전압이 될 때도 있고, 어떤 때는 드레인 전류가 전혀 흐르지 못하는 분기점 전압도 된다는 점 때문에 난해 해 진다. 어찌보면 서로 모순되어 보이는 현상을 일으키는 전압이 똑 같이 핀치 오프전압이 될 수 있는가!!

서로 이질적인 현상을 일으키는 전압을 동일하게 핀치 오프전압 이라고 했는지 궁금해한 사람도 있을 것이지만 현실적으로 속 시원하게 설명해 준 곳은 찾기 어렵다. 문제 의식조차 없었던 것도 사실이다.모순해결의 관점에 맞추어 설명을 읽어 보면 작은 도움이 될 것 같다.

MOSFET에 비해서는 활용도가 떨어지나 JFET의 동작 특성과 용도를 알면 여러 종류의 FET를 대충 파악 할 수는 있게 된다. 많이 널리 선호되는 소자는 MOSFET 이다. 그러나 기본기의 시작은 JFET 부터다. P 와 N 채널이 있는데 N채널을 중심으로 설명을 한다.

아래 그림의 JFET에서 보는 바와 같이 P 와 N의 접합 부근에서는 다이오드의 PN접합과 같이 공핍층 형성이 자연스럽게 된다. 이런 공핍층을 확산에 의해 생겼기 때문에 확산 공핍층이라고 구별해 불러주는 곳도 있다. JFET 특성을 파악하기 위해서 전압을 인가해 주는데, 바이어스 ( Bias : 직류전압을 건다 )를 거는 것은 드레인-소스 간( VDS ) 게이트-소스간의 전압( VGS )을 걸어 주게 된다.

두 전압을 서로 변화 시키면 변수가 두 개가 되어 뇌가 따라가기 복잡하기 때문에 두 군데 전압을 변화시키는 것 보다 한 군데는 고정으로 전압을 인가하고, 한 군데 전압을 변화시켜 어떤 특성이 보이는지 고려해 줘야 사고하는데 쉽다.

먼저 게이트-소스간 전압을 0V로 고정시키고, 드레인-소스 간 전압( VDS )을 증가하는 방향으로 변화 시키면서 어떤 특성을 뽑아 낼 수 있는지 지켜본다. 출력쪽 전압을 증가시켜가면서 출력의 전류를 추적해 내는 것을 출력특성 이라고 해 준다.

① 게이트-소스간 전압( VGS )을 0V로 고정시키고, 드레인-소스 간 전압( VDS )을 인가하지 않는다.

드레인과 소스간의 전류 ( ID ) 가 흐르지 않는다.

② 게이트-소스간 전압( VGS )을 0V로 그대로 고정시키고, 드레인-소스 간 전압( VDS )을 증가시키면서 인가 한다.

드레인과 소스간의 전류 ( ID ) 가 흐르기 시작하는데 드레인-소스 간 전압( VDS )이 증가하는 것에 비례 해서 증가한다. 증가선을 이상화 시켜 선형적으로 증가하는 것으로 간주해 준다. 그런데 여기서 JFET의 구조가 어떻게 변하는가를 주목해야만 한다. 드레인-소스 간 전압( VDS )이 증가하는 것에 맞추어 드레인과 게이트 간에는 역방향 전압이 점점 강해지므로 마치 다이오드의 PN 접합처럼 역방향 바이어스가 증가되면 공핍층이 증가된다.

게이트와 소스간에 존재하던 공핍층이 크게 점점 자라나기 시작한다. 이 때는 확산에 의한 공핍층으로 부터 더 증가하게 되는데, 이는 직류전압 ( 바이어스 )를 걸어 주었기 때문에 일어난 현상이었다. 그래서 이때의 공핍층을 바이어스 공핍층이라 세분해 준다.

③ 게이트-소스간 전압( VGS )을 0V로 계속 고정시키고, 드레인-소스 간 전압( VDS )을 이전 상태 보다 증가시키면서 인가 한다.

드레인과 소스간의 전류 ( ID )의 추세가 계속 증가하는 방향으로 커진다. 게이트와 소스간에도 공핍층이 더 크게 확대된다.

④ 게이트-소스간 전압( VGS )을 0V로 끝까지 고정시키고, 드레인-소스 간 전압( VDS )을 더욱 높여 인가해 가기로 한다.

드레인-소스 간 전압( VDS )을 어느 순간까지 높여가다 보면 드레인과 소스간의 전류 ( ID )는 더이상 증가하기를 포기하고 거의 평탄해 지는 구간이 생기게 된다. 또한 이때 JFET의 상태를 보면 게이트 부분에서부터 자라 나가던 공핍층 양쪽이 한 점에서 서로 맞닿는 현상이 발생하게 된다. 이 때를 가리켜서 핀치오프 ( Pinch-off ) 상태가 되었다고 지칭해 준다.

핀치오프 이후에 편의상 특성 곡선이 평탄하다고 했는데 실제로는 약간의 기울기를 가지고 상승하는 추세를 그린다.

핀치 오프 ( Pinch-off )라는 말은 아래 그림과 같이 엄지와 검지를 맞잡았을 때, 마치 한 점에서 두 손가락이 마주치는 것처럼 되는 형태를 의미한다.

그런데 이 지점에서 이해하기 어려운 점이 딱 버티어 우리를 곤란하게 만든다. 위의 실험에서 그래프를 보면 드레인과 소스간의 전류 ( ID )는 증가하지 않지만 계속 일정하게 흐르는 것을 볼 수 있는데, 우리의 편견으로는 어떻게 공핍층이 생기는데 전류가 흐를 수 있냐는 것이다. 전류가 흐르지 않는 상태로 다이오드의 역방향 바이어스에 순치된 우리의 이성은 '공핍층= 절연체 일 것'이라는 편견에 찌들어 여기서부터 헤메이게 되었던 것이다. 핀치오프 ( Pinch-off ) 이후로는 채널이 막혀 전류가 전혀 흐를것 같지 않은데 어떻게 전류가 흐른단 말인가?

어떤 사람들에겐 이게 고민이고 풀리지 않는 숙제 같은 부분이다.

다이오드의 역방향 바이어스로 인한 공핍층과는 다른 변수가 있다 그것이 무엇일까? JFET의 동작에서 핀치오프 ( Pinch-off ) 현상이 일어날 때의 구조를 다시 한번 검토해 보자.

증가하는 드레인-소스 전압에 의해 핀치오프가 걸린 때는 드레인과 게이트 사이에는 공핍층이 서로 맞닿아 , 드레인과 소스사이에 전류가 흘렀던 채널이 공핍층으로 막힌 것이 분명하지만, 드레인과 소스 사이에는 강한 전압이 걸려 전계가 작용하고 있다는 사실을 염두에 두어야 한다.

강한 전계가 작동하고 있다는 것은 전자가 공핍층을 재빠르게 건너가 버릴 수 있는 유인책이 아주아주 충분하다는 의미를 갖는다. 마치 이루어 질 수 없는 남녀간의 사랑이 음력 칠월 칠석 까마귀, 까치가 만들어 준 오작교( 烏鵲橋 )로 견우와 직녀가 만나는 것처럼 전압 ( 전계 )은 마치 오작교의 역할을 수행 한다고 생각하면 된다. 강한 사랑은 국경을 초월 하듯이 반도체에도 이와 비슷한 현상이 있는 셈이다.

그렇다면 이런 느닷없이 보이는 주장은 근거가 있는가? 그렇다 우리는 이미 BJT 동작특성을 공부할 때, 어떤 조건이 성립만 하면 공핍층도 뚫어 버리고 지나가는 전자에 대해 전제하고 있었다. BJT를 활성영역에서 동작시키기 위해 아래와 같이 직류전압을 걸었다는 것을 상기 하기 바란다.

일단 베이스-컬렉터 사이에 공핍층이 보이는가?

베이스와 에미터 사이는 순방향 바이어스이기 때문에 에미터에 있는 전자가 뭉텅이 채 베이스로 건너간다. 반도체 제작 공정상 베이스는 얇게 만들고 불순물 농도를 에미터 보다 낮게 가져 간다. 베이스영역에 있는 낮은 농도의 정공과 재결합한 전자를 제외하고 에미터로 부터 대거 이주한 전자는 짝이 없는 홀아비 처럼 갈데라고는 베이스-컬렉터 단의 공핍층 쪽 밖에 없게 된다.

이런 공핍층을 건너는데에는 강력한 유인이있어야 비로소 가능해 진다. 루비콘 강을 앞에 두고 카이사르가 황제의 야망을 불태우면서 건너 갔듯이 전자는 컬렉터 쪽에 +전압에 의한 강력한 전계로 인해 질풍노도( 疾風怒濤 )와 같이 공핍층을 건너 갈 것이다. 해답은 강력한 전압에 의한 전계가 있어야 전자가 공핍층을 뚫고 지나갈 수가 있다. BJT와 마찬가지로 JFET도 핀치오프 이후로 이런 현상이 발생하는 것이다. 그래서 반도체소자는 비슷한 면이 있는 것 같아 보인다. 그렇다고 공핍층을 도체라고 간주하면 오해 중의 오해이다.

이런 사정이라면 MOSFET의 Depletion 형과 Enhancement 형도 비슷한 동작을 할 것으로 기대 해도 된다. 기본적 동작 하나를 알면 나머지는 거져 먹기식이 된다. 전위차가 존재한다면 전자는 공핍층을 빠르게 가로질러 간다는 명제하나 기억하기로 한다.

댓글 영역